The inherent simultaneous operations in the physical chip is mimicked in the language by always (most commmon), initial and fork/join blocks. There is always a “module” at the top-level representing the chip structure (for synthesis), and one at the system level for verification. The number of entities and interconnects do not change dynamically. Modules (module), Ports(input/output/inout), connections (wires), blocks registers (reg) are all fixed at compile time.

Its structure and main principles ( as described below ) are designed to describe and successfully implement an electronic system.Īn electronic circuit is a physical entity having a fixed structure and Verilog is adapted for that.

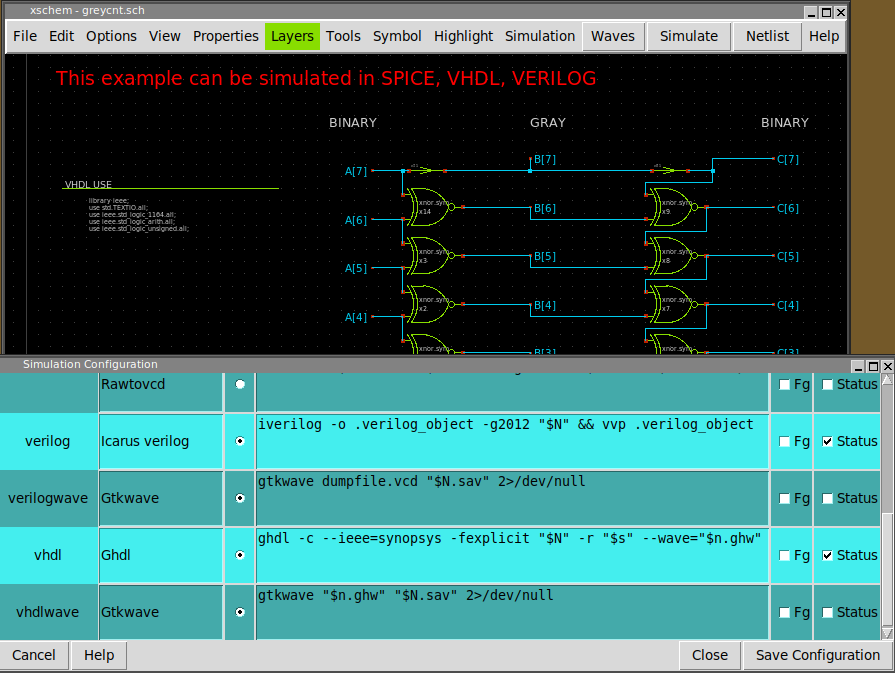

#GTKWAVE TUTORIAL VERIFICATION#

It is also used in the verification of analog circuits and mixed-signal circuits. It most commonly describes an electronic system at the register-transfer level (RTL) of abstraction. Verilog is a hardware description language (HDL) used to model electronic systems. In simulation (not typically in synthesis), wire variables may be in one of four states: 0, 1, floating ( z), and undefined ( x).ĭetailed instructions on getting Verilog set up or installed is dependent on the tool you use since there are many Verilog tools.Designs are hierarchical, with the ability to instantiate modules that have a desired behaviour.Variables must be declared as either single-bit wide or with an explicit width.There are two types of assignment, blocking and non-blocking, each with their own uses and semantics.It is noteworthy for a reasons that distinguish it from “traditional” programming languages: Verilog is a hardware description language (HDL) that is used to design, simulate, and verify digital circuitry at a behavioral or register-transfer level.

Verilog Getting started with verilog Remarks #